Hi all,

I am using the RFSoC4x2 with PYNQ v3.1.1.

I am trying to capture 1 ms of ADC samples on all ADC channels with sample times synchronized across multiple channels. I think the easiest way to do that with pre-existing firmware is through the MTS overlay. However, the max number of samples in the overlay is 2^16 which corresponds to ~16 us.

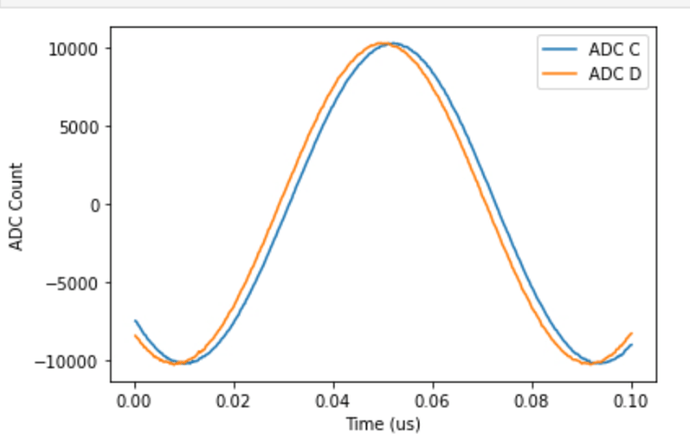

One way to increase the total sample time is to increase the size of the BRAM the RFDC writes to. I was able to increase the size from 128K to 512K for each ADC BRAM in Vivado without it telling me I’ve ran out of BRAM blocks. When testing it out, this allows me to write 2^18 samples now, but it also seems to introduce a constant offset of ~2 ns between ADC channels C and D on the same tile. I am calculating this offset by splitting the same 12 MHz sine wave into each channel and fitting for the phase difference between the two.

Moreover, the offset is constant in magnitude but seems to change sign randomly, going from 2 ns to -2 ns and back and forth. Comparing this with the expected behavior of 128K BRAMs, there is indeed a constant offset between channels C and D, but it doesn’t change sign and is appreciably smaller at ~25 ps.

Does anyone know what could be going on? I would prefer no O(10 ps) offsets, but don’t mind calibrating out O(1 ns) offset – it’s just the sign-flipping back and forth which is a problem. I am happy to provide the bitstream and my code. Please see the figures below.

512K BRAM test 1

512K BRAM test 2 (note ADC C now lags ADC D)

Thanks,

Cameron