DMA issue that might be due to software initialization

I think this is a PYNQ problem, not a Xilinx problem. What I have is a very simple design with the ZYNQ block, connected to 2 DMA blocks. One of the blocks reads from DDR and streams into an AXI fifo (so only the READ port is enabled), the other reads from the fifo and writes into DDR (so only the WRITE port is enabled). This is basically the same project as in the tutorial:

with a few minor changes, and updated using the RealDigital 4x2 gen 3 RFSoC and Vivado 2024.2.

In PYNQ, I load the project via Overlay(), and set up the base pointers to the two DMA engines and immediately print out the control and status registers. I’m looking at the documentation here:

and on page 27 it describes the control register bits and on page 29 the status register. On page 28 it says that bit 1 of the control register is reserved and will always be read as a 1.

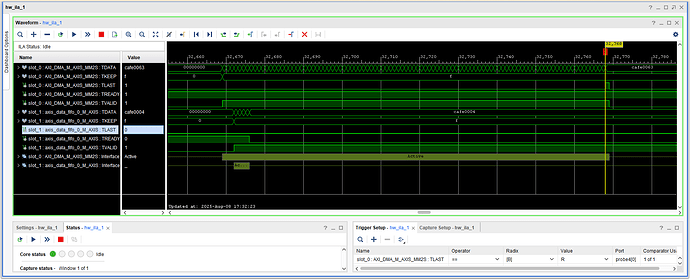

What I find is that for the DMA that only reads from DDR, the control register comes up 0x0 and the status register also 0x0. Which is what I expect for status but I would have expected control to come up as 0x2.

For the DMA the takes data from the fifo (over AXIS stream) and writes into DDR, the status register comes up 0x0 as expected but the control register comes up 0x10003. Bit 1=1 which is what I expected, but bit0=1 which means DMA is running. And bit 16=1 which has something to do with interrupts, which I don’t enable (and don’t know HOW to enable!).

I asked chatgpt about this, and it agreed that 0x10003 was “wrong” and then said

"This almost certainly came from auto-generated init scripts or Python overlay code

Of course, it’s just a stupid computer program.

Anyway, I’m wondering if this has something to do with the fact that the DMA that has the WRITE port enabled is looking at a FIFO output, and maybe somehow it’s getting turned on when the FIFO AXI ready is asserted? Could it be something like that?

Does anyone have any advice?

Thanks!

Drew