Consider this set of constraints:

##IO outputs

set_property -dict { PACKAGE_PIN T14 IOSTANDARD LVCMOS33 } [get_ports { IO_PORT[0] }]; #IO_L5P_T0_34 Sch=ck_io[0]

set_property -dict { PACKAGE_PIN U12 IOSTANDARD LVCMOS33 } [get_ports { IO_PORT[1] }]; #IO_L2N_T0_34 Sch=ck_io[1]

##SYNC output

set_property -dict { PACKAGE_PIN U13 IOSTANDARD LVCMOS33 } [get_ports { SYNC_PORT[0] }]; #IO_L3P_T0_DQS_PUDC_B_34 Sch=ck_io[2]

##IO inputs

set_property -dict { PACKAGE_PIN V13 IOSTANDARD LVCMOS33 } [get_ports { IO_PORT_I[0] }]; #IO_L3N_T0_DQS_34 Sch=ck_io[3]

set_property -dict { PACKAGE_PIN V15 IOSTANDARD LVCMOS33 } [get_ports { IO_PORT_I[1] }]; #IO_L10P_T1_34 Sch=ck_io[4]

set_property -dict { PACKAGE_PIN T15 IOSTANDARD LVCMOS33 } [get_ports { IO_PORT_I[2] }]; #IO_L5N_T0_34 Sch=ck_io[5]

set_property -dict { PACKAGE_PIN R16 IOSTANDARD LVCMOS33 } [get_ports { IO_PORT_I[3] }]; #IO_L19P_T3_34 Sch=ck_io[6]

set_property -dict { PACKAGE_PIN U17 IOSTANDARD LVCMOS33 } [get_ports { IO_PORT_I[4] }]; #IO_L9N_T1_DQS_34 Sch=ck_io[7]

set_property -dict { PACKAGE_PIN V17 IOSTANDARD LVCMOS33 } [get_ports { IO_PORT_I[5] }]; #IO_L21P_T3_DQS_34 Sch=ck_io[8]

set_property -dict { PACKAGE_PIN V18 IOSTANDARD LVCMOS33 } [get_ports { IO_PORT_I[6] }]; #IO_L21N_T3_DQS_34 Sch=ck_io[9]

set_property -dict { PACKAGE_PIN T16 IOSTANDARD LVCMOS33 } [get_ports { IO_PORT_I[7] }]; #IO_L9P_T1_DQS_34 Sch=ck_io[10]

set_property -dict { PACKAGE_PIN R17 IOSTANDARD LVCMOS33 } [get_ports { IO_PORT_I[8] }]; #IO_L19N_T3_VREF_34 Sch=ck_io[11]

set_property -dict { PACKAGE_PIN P18 IOSTANDARD LVCMOS33 } [get_ports { IO_PORT_I[9] }]; #IO_L23N_T3_34 Sch=ck_io[12]

set_property -dict { PACKAGE_PIN N17 IOSTANDARD LVCMOS33 } [get_ports { IO_PORT_I[10] }]; #IO_L23P_T3_34 Sch=ck_io[13]

The “##IO outputs” and “##IO inputs” sections work as intended, whereas the “##SYNC output” is not, although the port is setup the same way as “##IO outputs” in block diagram.

Work as intended means, I generate outputs on the two “##IO outputs”, I connect them to any of the “##IO inputs” and it reads correct gpio value. On the sync port, I generate 0’s and 1’s as well but when connecting this port to any of the inputs, it always read 0.

Note: previously the “PACKAGE_PIN U13” was included in the “##IO inputs” port list, but when I realised I need another output for sync, I set this one on SYNC_PORT and renumbered all of the “##IO_PORT_I” indices 0-10, (instead of previously 0-11). Now, is it possibly somehow that Vivado cached and is now causing problems?

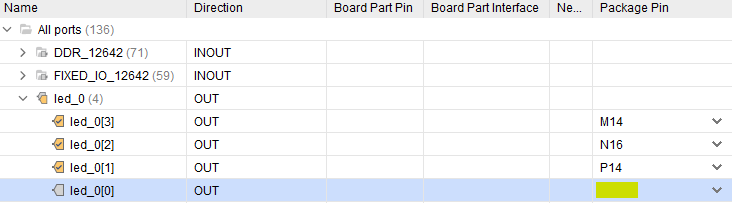

block diagram looks like this: